篮球买球下单平台空隙数据处理需求成为首要任务-押注篮球的app_平台入口

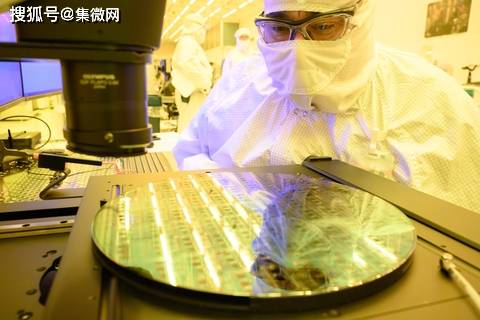

半导体产业恒久以来依赖平面放松时刻来提高性能篮球买球下单平台,但这一法子正逐步贴近物理极限。面临东谈主工智能应用需求的迅猛增长,英特尔、台积电和三星等半导体巨头正加快研发转变惩处决策,以期空隙下一代计算开垦的需求。其中,3D IC时刻已成为这些大厂计谋布局的关节一环。

连年来,AI大模子的兴起为3D IC时刻的快速发展提供了前所未有的机会。3D IC通过垂直堆叠芯片并诈欺硅通孔(TSV)时刻,竣事了电子元件的高密度三维集成,与2.5D封装、Chiplet、扇出型封装等先进封装时刻一齐,成为后摩尔时间提高芯片性能的首要技能。相较于其他时刻,3D IC更侧重于高性能计算场景,而其他时刻则更把稳天真性与资本效益的均衡。

各泰半导体厂商早已涉足3D IC时刻的研发,但AI大模子的旺盛发展无疑为这一限制注入了新的活力。台积电高档副总裁张晓强指出:“为了为客户提供圆善的产等第惩处决策,晶体管时刻和先进封装集成必须并行发展。3D架构时刻组合对咱们来说已变得至关首要。”

英特尔代工业务的高档副总裁Kevin O’Buckley相通强调了3D IC时刻的首要性:“跟着内核数目的加多和计算性能的不停提高,空隙数据处理需求成为首要任务。3D时刻便是一个很好的例子,咱们不错诈欺芯单方面积的大部分来放弃SRAM,而无须松手用于计算的芯单方面积。”

尽管3D IC时刻显贵裁汰了元件间的物理距离,提高了芯片性能并斥责了功耗,但这一法子也带来了更为复杂的子系统需求,在制造工艺、材料科学和联见解子上齐建议了新的挑战。TSV行动3D堆叠的关节时刻之一,其工艺径直影响互连密度与良率,需要不停冲破更高的深宽比极限。

在制造工艺方面,更先进的等离子刻蚀时刻不停表现,或者竣事更高的深宽比和更精准的孔体式为止。在材料方面,除了传统的铜材料外,新的低电阻、高可靠性导电材料如合金材料和碳纳米管复合材料等正在研发中,有望进一步斥责信号传输损耗。芯片对芯片键合时刻也至关首要,刻下的琢磨要点聚合在提高键合精度、速率与可靠性上。

台积电在3D IC限制变成了以SoIC为中枢的时刻体系,勾搭CoWoS和硅光子时刻,掩饰了从逻辑堆叠到异构集成的全链条。行动SoIC的首发客户,AMD通过SoIC与CoWoS勾搭,竣事了带宽向上5TB/s的AI芯片。台积电正在开发SoIC 2.0时刻,打算将互连节距从刻下的9μm放松至5μm,并引入后头供电时刻以提高电源效用和散热才略。

英特尔则以Foveros为中枢时刻,勾搭EMIB和PowerVia时刻,变成了掩饰逻辑堆叠到异构集成的圆善时刻体系。Foveros通过羼杂键合和TSV时刻竣事芯片垂直堆叠,维持高密度集成。英特尔正开发Foveros 2.0时刻,打算相通是将互连节距放松至5μm,并引入后头供电时刻。英特尔还在积极开发光分解时刻以增强3D IC产物的性能。

三星则以X-Cube为中枢时刻,在3D IC限制竣事了从逻辑堆叠到异构集成的掩饰。X-Cube通过硅通孔和羼杂键合时刻竣事芯片垂直堆叠。在热治理时刻方面,三星正在开发微流体冷却时刻,通过在芯片里面镶嵌微米级冷却通谈篮球买球下单平台,将散热效用较传统风冷提高3倍。三星还在开发光学I/O时刻,并有计划将3D IC与下一代制程时刻勾搭,以竣事更好的协同恶果。